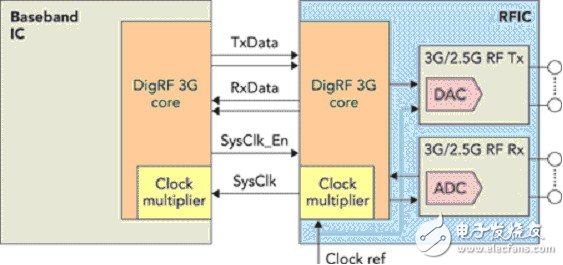

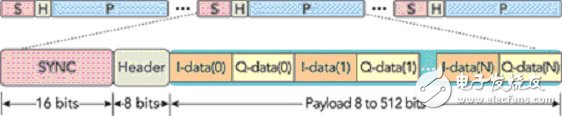

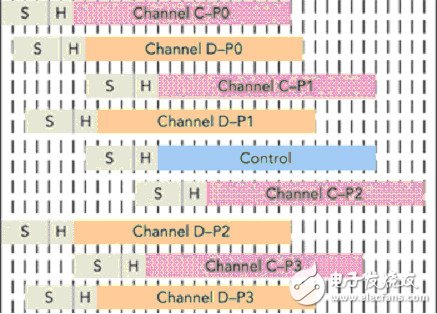

DigRF is set to replace the two dominant methods of communication between RF and baseband chips: analog signaling and proprietary digital signaling (either parallel or serial). The MIPI Alliance is driving the shift from various I/Q signaling interfaces toward a standardized, packet-based digital serial interface using the DigRF standard. A working group within MIPI has developed the DigRF specification for 2.5G and 3G handsets, with future versions expected to support higher data rates required by 4G technology. Adopting the DigRF interface gives designers greater flexibility in selecting components. For example, a designer might source an expensive baseband IC from one vendor while choosing RF, power management, and other modules from different suppliers. However, this increased flexibility also introduces challenges, particularly in testing strategies, as general-purpose devices can complicate automated test procedures. During RF reception testing, the main goal remains the same as before DigRF: capturing I/Q data, applying custom digital signal processing algorithms, and recording results to determine device performance. But compared to older RFICs, DigRF devices may add significant overhead during production testing. Engineers must find ways to reduce this overhead, which is a major challenge when designing automated test systems for mass production. Understanding the DigRF interface begins with its minimal signal requirements. For a basic phone configuration, only six wires are needed (Figure 1). The RxData/TxData signal carries I/Q data along with control and status messages in a packet format. Figure 1. A basic DigRF phone setup requires just six wires. Data transmitted via DigRF is encapsulated in protocol packets or frames. Each frame consists of three parts: sync, header, and payload (Figure 2). Every packet starts with a 16-bit synchronization sequence, used by the receiver to align the real-time strobe phase for each frame. Following the sync, the next 8 bits form the header, which defines the payload's role and content. The header itself includes three sections: 3 bits for payload size, 4 bits for Logical Channel Type (LCT), and 1 bit for Clear to Send (CTS) signaling. Figure 2. The DigRF 3G data frame starts with a 16-bit sync sequence, followed by an 8-bit header and I/Q data. The payload size varies across different packets, leading to varying levels of coding overhead. The LCT determines whether the payload contains control data or I/Q data, while the CTS allows the RF device to manage the data stream from the baseband during transmission. The remaining N bits in the frame contain the actual data being transmitted. For instance, in non-diversity mode, the RxData frame uses channel C with a 256-bit payload, containing alternating I and Q data. DigRF 3G supports three timing modes for digital transmission, depending on the type of RF information being sent (Table 1). It also supports three common reference clock frequencies (19.0 MHz, 26.0 MHz, and 38.4 MHz), which are delivered to the baseband through the SysClk signal. Regardless of the speed mode, the DigRF processor manages the data stream using a local FIFO buffer, producing unpredictable timing when transmitting frames. One of the key challenges in testing DigRF devices is managing the uncertainty in the RxData packet during RF reception tests. Multiple levels of uncertainty exist in the synthesis state of the RxData signal, including phase timing, frame timing, frame type, and the data within the payload. The 312 Mbps data rate comes from a 1/4 division of a 1248 MHz master clock, typically generated by a PLL. In a production test system, the clock input to the device should be provided by the RF instrument, taking into account the impact of phase noise on the RF front end. The starting phase of this clock source is usually uncontrollable compared to a typical digital subsystem. The DUT’s input clock phase is unknown, and the phase generated by the PLL multiplier/divider is also uncertain. This combination leads to unpredictable RxData output timing, including during power-on cycles and across multiple devices in a test configuration. A production tester must be capable of maintaining digital subsystem operation while making necessary hardware and DUT adjustments between tests. This ensures that the tester can maintain strobe timing relative to the DUT output, avoiding phase retuning during formal testing and reducing overall test time. Another critical challenge is handling multi-level uncertainty in packet transmission performance. As shown in Figure 3, during each RF receive test, the tester does not know when or what type of packet will be transmitted, or if it matches the expected format (e.g., an active control status message from the RFIC). Jiangsu Qilong Electronic Technology Co., Ltd. , https://www.qilongtouch.com